# Neo900 Hackerbus

### PRELIMINARY - SUBJECT TO CHANGE WITHOUT FURTHER NOTICE

Jörg Reisenweber\*, Werner Almesberger<sup>†</sup>

February 11, 2016

The Hackerbus is an interface that allows user-provided circuits to connect directly to power rails and various signals in the Neo900.

Warning: Hackerbus gives access to signals that can upset the operation of the Neo900 and incorrect use may cause permanent damage inside and outside the device. Use with caution!

Characteristics beyond what is specified in this document should be obtained by examining the schematics and the data sheets of the respective components.

<sup>\*</sup>Concept and design requirements.

<sup>&</sup>lt;sup>†</sup>Specification details and illustrations.

# 1 Pin assignment

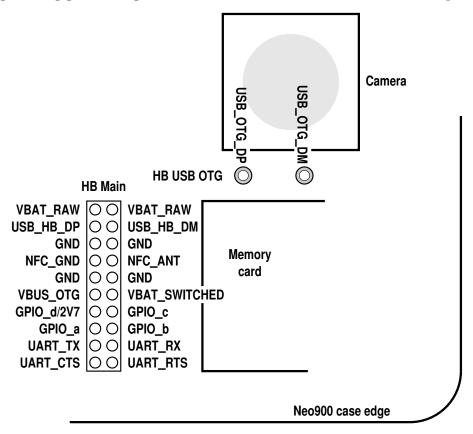

Hackerbus uses two connectors, one for power and various signals and one for USB OTG data, which are arranged around the memory card on the Break-Out-Board (BOB).

The following drawing gives a rough overview of connector locations and shows the pin assignment:

The following table describes the functions of the pins on the Hackerbus main connector:

| Hackerbus pin                              | Description                                                          |  |  |

|--------------------------------------------|----------------------------------------------------------------------|--|--|

| VBAT_RAW                                   | Direct connection to the battery (charging allowed)                  |  |  |

| VBAT_SWITCHED                              | Like VBAT_RAW but switched off when system is powered down           |  |  |

|                                            | Reverse-feed <u>not</u> allowed!                                     |  |  |

| $VBUS\_OTG$                                | USB OTG bus voltage (reverse-feed allowed)                           |  |  |

| GND                                        | System ground and return for power and all signals but NFC and audio |  |  |

| USB_HB_DP                                  | USB differential data, positive                                      |  |  |

| USB_HB_DM                                  | USB differential data, negative                                      |  |  |

| UART_TX                                    | UART3, Transmit data (output from CPU)                               |  |  |

| $UART_RX$                                  | UART3, Receive data (input to CPU)                                   |  |  |

| $UART\_CTS$                                | UART3, Clear To Send (input to CPU)                                  |  |  |

| $UART_RTS$                                 | UART3, Ready To Send (output from CPU)                               |  |  |

| GPIO_a                                     | TBD                                                                  |  |  |

| GPIO_b                                     | TBD                                                                  |  |  |

| $GPIO_c$                                   | TBD                                                                  |  |  |

| $\mathrm{GPIO}_{-\mathrm{d}}/2\mathrm{V7}$ | TBD / 2.7 V rail                                                     |  |  |

| NFC_ANT                                    | NFC antenna, positive                                                |  |  |

| $NFC\_GND$                                 | NFC antenna, ground or negative                                      |  |  |

|                                            | Do not connect to any other GND!                                     |  |  |

Note that the UART signals may also be used as general IOs and that their role further depends on the configuration of the infrared (IR) subsystem [1].

**TO DO:** The exact function of UART\_RX will depend on the implementation of IR RX, which will be decided at a later time.

The Hackerbus USB OTG through-hole pads give access to signals from the Neo900 Micro USB connector:

| Hackerbus pin  | Description                     |

|----------------|---------------------------------|

| USB_OTG_DP     | USB differential data, positive |

| $USB\_OTG\_DN$ | USB differential data, negative |

Further details on how Hackerbus connects to USB can be found in section 3.

# 2 Alternate pin assignments

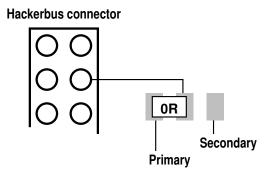

Some pins have an alternate assignment that can be selected by moving a jumper on the Neo900 PCB. The jumper consists of three pads and a 0  $\Omega$  resistor that is soldered in the position that selects the primary function, as shown below:

The user can unsolder the resistor and either re-solder it such that it connects to the secondary function, or use jumper wires for any other type of connection.

| Jumper | Primary | Secondary        |

|--------|---------|------------------|

| Rxxx   | TBD     | I2C #3 SDA       |

| Rxxx   | TBD     | I2C #3 SCL       |

| Rxxx   | TBD     | Audio out, left  |

| Rxxx   | TBD     | Audio out, right |

| Rxxx   | TBD     | Audio ground     |

| Rxxx   | TBD     | USB OTG ID       |

Please note that the secondary functions have ESD protection but only the two I2C signals have level shifters.

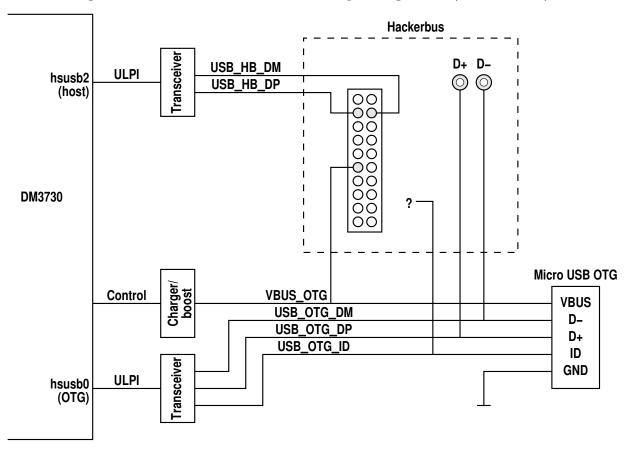

### 3 USB access

Hackerbus gives access to two USB buses: the data signals of a High-Speed host port are available on the Hackerbus connector. This USB port is used exclusively for Hackerbus.

Furthermore, the data signals of the Neo900 USB OTG port (High-Speed) are available on contacts accessible from the Hackerbus, VBUS of the OTG port is available on the Hackerbus connector, and the ID signal of OTG is available as an alternate pin assignment. (See section 2.)

**TO DO:** Define and indicate alternate pin assignment for USB ID.

Note that there is no bus supply voltage (VBUS) on the dedicated USB interface of Hackerbus. User circuits can be powered from the 2.7 V rail or from any of the other supplies.

# 4 Physical placement

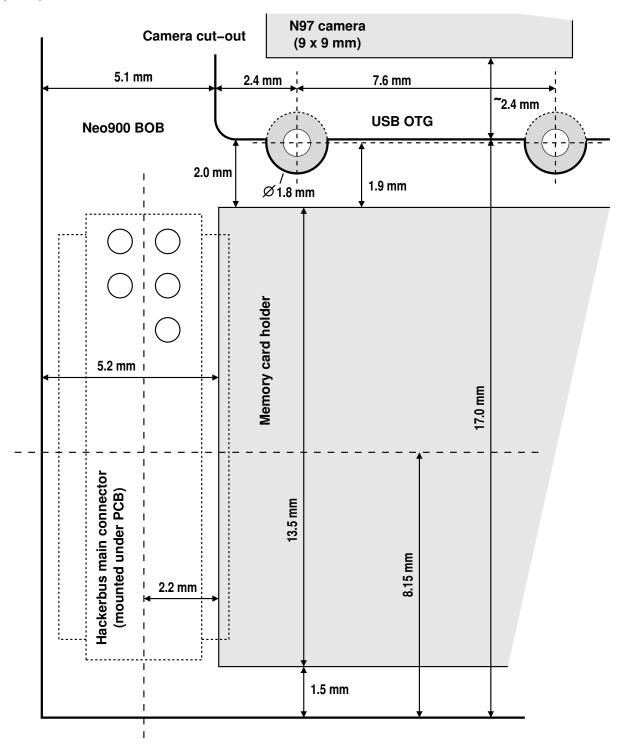

The following drawing illustrates the precise placement of components on the Break-Out-Board (BOB):

The main connector is soldered to the bottom of the BOB and the header pins pass through holes in the PCB, entering the receptacle from the bottom. The USB OTG contacts are on the LOWER board of Neo900 and can be accessed through an opening in the BOB.

Please note that the Hackerbus connector and contacts are covered by plastic structures in the N900 case and are therefore only accessible when the case is removed or if the respective plastic structures have been cut.

#### 4.1 Hackerbus main connector

On the Neo900 side, the principal connector for Hackerbus is a Harwin M50-3151042 [2] female connector with 20 contacts organized in a  $10 \times 2$  array. The connector has a 1.27 mm pitch and is mounted underneath the Neo900 break-out board (BOB).

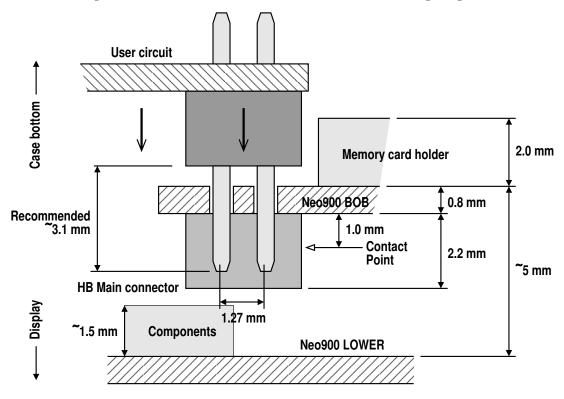

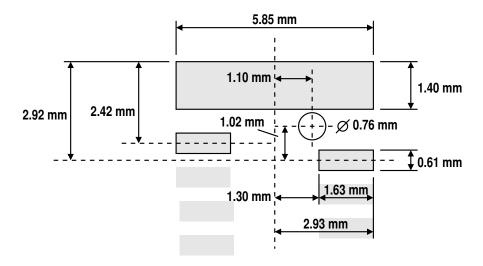

The vertical stacking of the main connector is illustrated in the following diagram:<sup>1</sup>

The male header shown as an example in the drawing has the dimensions of the FCI 20021111-00020T4LF through-hole connector,<sup>2</sup> with a contact length of 3.05 mm and a plastic mold height of 2.5 mm. (See also [3].)

<sup>&</sup>lt;sup>1</sup> The drawing is approximately to scale but dimensions drawn can be off by up to 0.15 mm in real-world coordinates.

http://portal.fciconnect.com/Comergent/fci/drawing/20021111.pdf

#### 4.2 Hackerbus USB OTG contacts

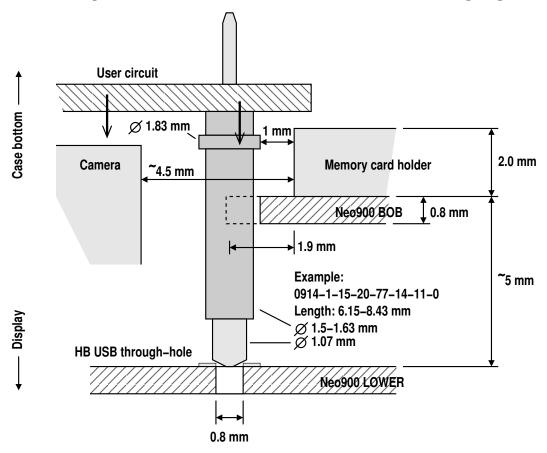

On the Neo900 side, the USB OTG contacts for Hackerbus consist of two through-hole pads in the LOWER board. Cut-outs in the BOB allow them to be accessed with pogo pins on the user board.

The vertical stacking of the USB OTG connection is illustrated in the following diagram:

The characteristics of the pogo pins depend on the placement of the user board. Clearances and hole diameters are designed for the Mill-Max 914 series. [4] The following table shows minimum, middle, and maximum length of the pogo pins in this series. The length corresponds to the distance between the facing sides of LOWER and the user board.

| Part number Length (mr           |      | nm)  |      |

|----------------------------------|------|------|------|

|                                  | Min. | Mid  | Max. |

| 0914- <b>0</b> -15-20-77-14-11-0 | 5.38 | 6.53 | 7.67 |

| 0914- <b>1</b> -15-20-77-14-11-0 | 6.15 | 7.29 | 8.43 |

| 0914- <b>2</b> -15-20-77-14-11-0 | 6.91 | 8.05 | 9.19 |

| 0914- <b>3</b> -15-20-77-14-11-0 | 7.67 | 8.82 | 9.96 |

### 4.3 Mechanical coupling with battery cover

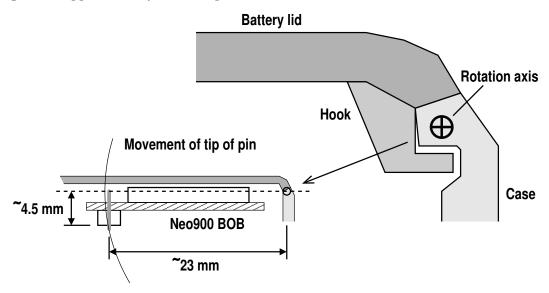

If the user circuit connecting to Hackerbus is mechanically coupled with the battery cover, the movement when opening and closing the battery compartment has to be considered. The following drawing shows approximately how the parts involved move:

The cover has a hook that goes into an opening in the case. When opening or closing the cover it rotates around that hook, which results in anything mechanically connected to the cover to perform the same rotation.

The drawing shows the path along which a header pin plugging into the Hackerbus main connector moves. This rotation may make it difficult to connect extensions whose Hackerbus connector is rigidly coupled with the battery cover. These difficulties would be more pronounced for the Hackerbus USB connector since it is closer to the axis around which the battery cover rotates.

Possible ways to avoid this issue include not coupling the extension with the battery lid, using a flexible coupling, or removing the hook on the cover.

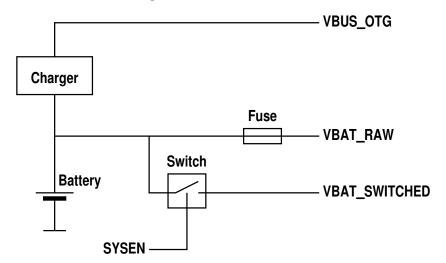

## 5 Overcurrent protection

To protect traces and other components from excessive current, VBAT\_RAW is equipped with a resettable fuse. Traces and contacts between battery and Hackerbus are designed to be able to permanently conduct at least the trip current of the fuse.

Note that the presence of this fuse does not guarantee that loads exceeding the trip current will not lead to malfunction. Furthermore, the battery is a user-provided item and needs to be evaluated separately by prospective users of VBAT\_RAW. The maximum current available on VBAT\_RAW depends not only on the fuse but also on the characteristics and condition of the battery.

The design of Neo900 is intended to support the following maximum currents without suffering damage or disturbing normal system operation, provided that suitable power sources are available:

| Hackerbus pin                              | Continuous current (A) |         |

|--------------------------------------------|------------------------|---------|

|                                            | Forward                | Reverse |

| VBAT_RAW                                   | 0.5                    | 1.5     |

| VBAT_SWITCHED                              | 0.3                    |         |

| VBUS_OTG                                   | 0.5                    | 0.5     |

| $\mathrm{GPIO}_{-\mathrm{d}}/\mathrm{2V7}$ | 0.1                    |         |

All these limits apply to individual rails. Predicting behaviour when drawing or injecting significant current on multiple rails at the same time is beyond the scope of this document.

Please note that none of these parameters are guaranteed, and further constraints may apply.

Peripherals using VBAT\_RAW should connect to both VBAT\_RAW contacts with traces that <u>each</u> are capable of carrying the full maximum current the application demands.

## 6 Level shifters

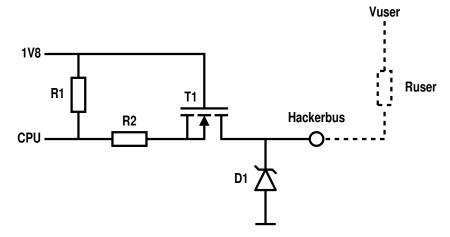

Level shifters are provided to interface with circuits operating in other domains than 1.8 V. The circuit is as follows, for each primary UART and GPIO signal:

The principle of operation is briefly described in [5] and further details can be found in [6]. R1 is usually an internal pull-up resistor in the CPU of 10 k $\Omega$  or higher. R2 limits the current when CPU and external circuit drive the Hackerbus signal in a conflicting way. R2 is 100  $\Omega$ . D1 protects against ESD and polarity inversion.

Note that our circuit differs from the NXP design in that Neo900 does not provide a pull-up resistor on the high-voltage side. If the user circuit needs a pull-up, e.g., to drive a logic input, it therefore has to provide one itself. If an external pull-up is to be used, it should be dimensioned such that it does not deliver more than 1.8 mA into the Neo900 if the corresponding Hackerbus signal is driven low (0 V). A value of  $10 \text{ k}\Omega$  or larger is recommended.

Power, NFC, USB, and secondary signals (other than I2C) are not equipped with level shifters.

Further limits and characteristics of this circuit are to be determined by the user.

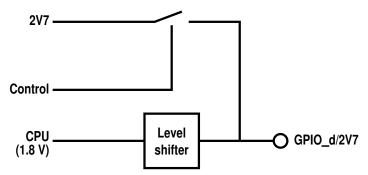

# 7 Switchable power rail

The 2.7 V power rail can be switched to the GPIO<sub>-</sub>d pin under software control. If not operating as power rail, GPIO<sub>-</sub>d can be used for regular IO. The following drawing illustrates the circuit:

The connection to the CPU is protected by the same circuit as all other IOs available on the Hackerbus. When GPIO\_d is configured as power rail, the CPU should set the corresponding GPIO to High-Z without pull-up or -down. The CPU may read the GPIO, but the resulting value is undefined.

**TO DO:** Determine whether we will use 2.7 V as described here or whether we have a spare LDO that could also provide other voltages.

### A LOWER-BOB connection

The design of Hackerbus also affects the connection between LOWER and BOB. We therefore discuss characteristics of the connection in this appendix, and provide a design that harmonizes with Hackerbus.

### A.1 Signals

In addition to the 20 signals of the Hackerbus main connector described in section 1, we have the following signals to other components on BOB:

| Signal(s)       | Number | Connects to                | Maximum average current |

|-----------------|--------|----------------------------|-------------------------|

| SD-CMD,CLK,DATx | 6      | Memory card holder         |                         |

| SD-VDD          | 1      | Memory card holder         | 100 mA (?)              |

| SD-CD           | 1      | Memory card holder         |                         |

| I2C-SDA,SCL     | 2      | Flash, camera cover sensor |                         |

| CAM-COVER       | 1      | Camera cover sensor        |                         |

| BATT-LID        | 1      | Battery lid sensor         |                         |

| 2V7             | 1      | Camera and battery sensor  | $50 \text{ mA}^3$       |

| USD-EN,INT,STR  | 3      | Flash controller           |                         |

| USD-VBATT       | 1      | Flash controller           | $1 A^4$                 |

| GND             | 1      | All of the above           | Sum of the above        |

|                 | 18     |                            |                         |

We expect that each contact of the board-to-board connector can support a maximum continuous current of 0.5 A (section A.3). This means that at least an additional pin should be assigned for flash use of USB-VBATT. With an additional ground pin as well, we therefore get a total of 20 contacts.

As described in section 5, Hackerbus can load VBAT\_RAW (which is the same as USB-VBATT) with an additional 1.5 A. We should therefore use at least a total of 5 pins for VBAT\_RAW and at least 6 pins for ground.

This brings the total number of contacts required to 40: 20 for Hackerbus plus another 20 for the remaining functions of BOB.

The MLX90248 hall switch for camera cover sensing has a maximum current consumption of 5 mA. The TMD2671 proximity sensor used on the battery lid has a supply current of 3 mA plus LED pulses of up to 100 mA with a duty cycle of  $^{7.2}$   $_{\mu s}/_{16.3}$   $_{\mu s} = 44\%$ .

Section "Current Limit" on page 16 of http://www.analog.com/static/imported-files/data\_sheets/ADP1653. pdf gives a maximum current of 2.1 A. If we assume a flash LED maximum continuous current of 240 m, a total forward voltage of 6.7 V, a battery fully discharged to 2.5 V, and a regulator efficiency of 80%, the resulting average current is 804 mA.

#### A.2 Connector characteristics

The most important parameter is the distance between boards. Measurements based on 3D scans of a N900<sup>5</sup> yielded an approximate distance of 5.2-5.3 mm between the bottom (i.e., the battery-facing side) of LOWER and the bottom of BOB. Given a PCB thickness of 0.8 mm, this means that we need connectors with a stacking height of approximately 4.4-4.5 mm.

To ensure precise placement of the connectors, positioning pins ("board guides") are desirable.

#### A.3 Connector selection

A Digi-Key catalog search yielded the following connector families with good availability of parts:

| Series                 | Stacked | Pitch | Current | Cycles     |

|------------------------|---------|-------|---------|------------|

|                        | height  | (mm)  | per pin | $(\max.)$  |

|                        | (mm)    |       | (A)     |            |

| FCI Conan <sup>6</sup> | 4.5     | 1.0   | 1.0     | 30         |

| Hirose $DF9^7$         | 4.3     | 1.0   | 0.5     | $30/100^8$ |

| Harwin $M40^9$         | 4.3     | 1.0   | 0.5     | 30         |

All three have a contacts in a trapezoidal arrangement with N contacts in one row and N+1 in the other, and very similar footprints. Positioning pins and solder retention are optional in some series:

| Series     | Positioning pin length | Solder retention |

|------------|------------------------|------------------|

|            | (mm)                   |                  |

| FCI Conan  | 0.5 mm, optional       | yes              |

| Hirose DF9 | 1.0 mm, optional       | optional         |

| Harwin M40 | 1.0 mm                 | yes              |

Hirose DF9 and Harwin M40 appear to have exactly the same geometry. FCI Conan has nearly the same contact arrangement, but the positioning pins are placed differently and the overall length is reduced. Note that the length of the positioning pins of DB9 and M40 exceeds the PCB thickness.

The stacking height of DF9/M40 (4.3 mm) matches the desired height of 4.5 mm within measurement and manufacturing tolerances. Conan matches the height exactly.

We will only consider connectors with at least 15 contacts and a footprint not exceeding the available PCB width of 17 mm.

<sup>5</sup> https://neo900.org/git/?p=scans;a=blob\_plain;hb=HEAD;f=data/stl/n900-rear-open-nobat-100um.stl.

http://portal.fciconnect.com/Comergent//fci/drawing/91900.pdf

http://media.digikey.com/pdf/Data%20Sheets/Hirose%20PDFs/DF9.pdf

<sup>&</sup>lt;sup>8</sup> Tin vs. gold plating.

http://cdn.harwin.com/pdfs/M40-600.pdf http://cdn.harwin.com/pdfs/M40-620.pdf

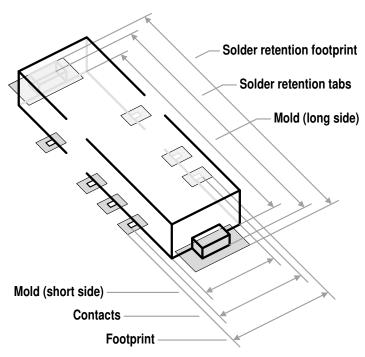

#### A.4 Connector dimensions

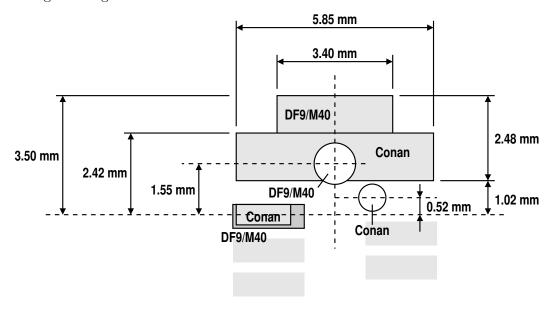

The following tables list the dimensions of the "bounding boxes" of the bodies and the footprints of the three connector families selected in the previous section. This stylized drawing illustrates the parameters we consider:

For the long sides we have the length of the body, and the edge-to-edge distance of metal tab and footprint of the solder retention. The body length is either the length of the plastic mold (in the case of Conan, where the mold protrudes) or the distance between the ends of the solder retention tabs (DF9/M40, where the tabs protrude), whichever is larger.

| Series     | Contacts | Body (mm) |           | Solder retention |

|------------|----------|-----------|-----------|------------------|

|            |          | Solder    | retention | footprint (mm)   |

|            |          | with      | without   |                  |

| FCI Conan  | 15       | 12.30     | _         | 11.84            |

|            | 21       | 15.30     | _         | 14.84            |

|            | 25       | 17.30     | _         | 16.84            |

| Hirose DF9 | 15       | 13.1      | 11.3      | 14.0             |

|            | 17       | 14.1      | 12.3      | 15.0             |

|            | 19       | 15.1      | 13.3      | 16.0             |

|            | 21       | 16.1      | 14.3      | 17.0             |

| Harwin M40 | 15       | 13.10     | _         | 14.00            |

|            | 21       | 16.10     | _         | 17.00            |

Only configurations with solder retention tabs and with 15 and 21 pins are available from more than one source.

For the short sides, we consider the width of the mold, the length of the protruding contacts (if any), and the edge-to-edge distance across the PCB pads for the contacts.

| Series     | Mold | Contacts | Footprint |

|------------|------|----------|-----------|

|            | (mm) | (mm)     | (mm)      |

| FCI Conan  | 5.59 |          | 5.85      |

| Hirose DF9 | 4.2  | 5.6      | 6.0       |

| Harwin M40 | 4.20 | 5.60     | 6.00      |

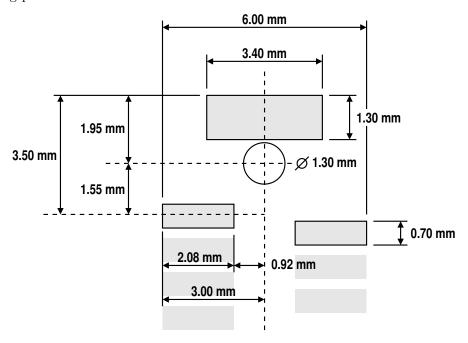

### A.5 Common footprint

With the above connectors, we have the choice between the common DF9/M40 design that would need a customization step (i.e., trimming of the positioning pins), and the less common Conan design that could be used without modification.

The following drawings illustrate the differences in footprint geometry and the location and size of the positioning pin:

DF9/M40 (above) is generally larger than Conan (below) and places the positioning pins on the center line.

From the above we can derive a common footprint design that should be able to accommodate either type of connector, permitting postponing the component choice until shortly before production and thus reducing sourcing risk:

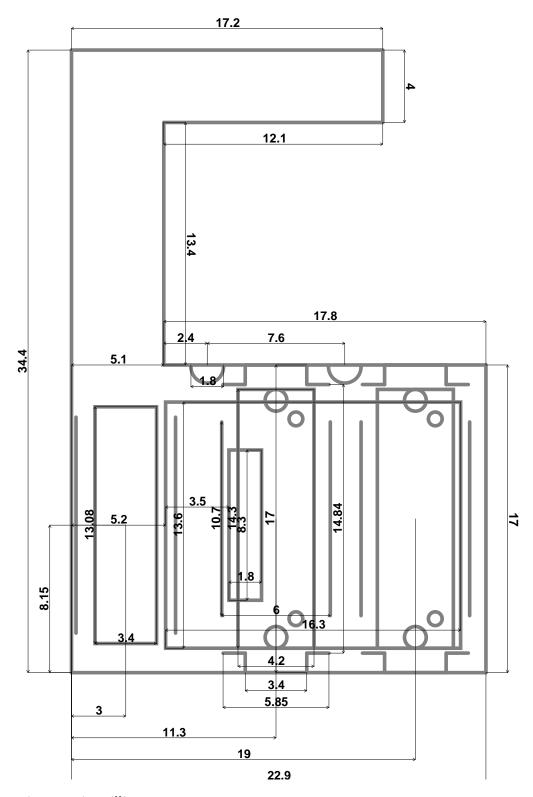

#### A.6 Placement overview

The following overview drawing shows the dimensions of BOB, the placement of the Hackerbus main connector (M50), the two board-to-board connectors (DF9/M40), and the memory card.

For each connector, the body is shown as a rectangle and additional lines mark the extent of protruding elements, such as pins or solder tabs. For the memory card, the bounding box and the pad area are shown.

All dimensions are in millimeters.

# A.7 Hypothetical pin assignment

To verify that all the required signals can be accommodated in a reasonable way, we provide a hypothetical pin assignment. This assignment is intended as a model reference only and should not constrain the pin assignment choices made for the actual circuit.

| Connector A                                                                             |                                                                                  | Connector B                                                                  |                                                                          |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| VBAT_RAW VBAT_RAW VBAT_RAW USB_HB_DM GND NFC_ANT GND VBAT_SWITCHED UART_TX UART_CTS GND | VBAT_RAW VBAT_RAW USB_HB_DP GND NFC_GND GND VBUS_OTG GPIO_d/2V7 UART_RX UART_RTS | GND CAM-COVER I2C-SDA USD-INT USD-EN SD-DAT1 SD-CD SD-CMD SD-DAT2 GPIO_a GND | 2V7 BATT-LID I2C-SCL USD-STR SD-DAT0 SD-CLK SD-VDD SD-DAT3 GPIO_c GPIO_b |

## **B** References

- [1] Reisenweber, Jörg; Almesberger, Werner. *GTA04b7 Infrared Subsystem*, August 2014. https://neo900.org/stuff/papers/ir.pdf

- [2] Harwin. 1.27mm pitch DIL SMT vert low-profile socket assy, M50-315XX42, March 2013. http://harwin.com/includes/pdfs/M50-315.pdf

- [3] Almesberger, Werner. Header Part Selection Overview, January 2016. http://neo900.org/stuff/papers/hdr.pdf

- [4] Mill-Max Mfg. Corp. Spring-Loaded Pins Discrete spring-loaded contacts, through-hole mount, https://www.mill-max.com/assets/pdfs/metric/025M.pdf

- [5] NXP Semiconductors. Level shifting techniques in I<sup>2</sup> C-bus design, AN10441, Rev. 01, June 2007. http://www.nxp.com/documents/application\_note/AN10441.pdf

- [6] Schutte, Herman. Bi-directional level shifter for I<sup>2</sup>C-bus and other systems, AN97055, August 1997, Philips Semiconductors Systems Laboratory Eindhoven. http://www.adafruit.com/datasheets/an97055.pdf